发布时间:2026-04-05

发布时间:2026-04-05  阅读次数:42次

阅读次数:42次

在实际应用中,晶振出现频率偏差、不起振或振荡不稳定的情况并不少见。很多时候,这些问题可能不是由晶振造成的,而是杂散电容。今天KOAN凯擎小妹聊一下杂散电容的来源、计算方法等。

杂散电容 Cstray

杂散电容是电路中天然存在的寄生参数。在实际设计中,杂散电容通常落在2pF~5pF之间,一般以3pF作为初始估算值。在导体(走线/地)、距离以及介质(PCB/空气),就会形成电容。杂散电容通常可近似看作由平行板结构和边缘电场共同形成的电容。如图所示:

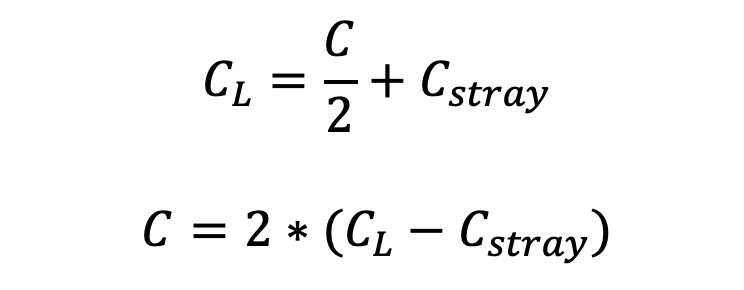

负载电容 CL

晶振的产品手册中给出的负载电容CL是晶振在标称频率下正常工作的关键参数。在典型的Pierce振荡电路中,当两侧电容采用对称设计(C1=C2=C)时,实际负载电容不仅取决于外接电容,还受到杂散电容Cstray的影响。

假设晶振的CL为18pF,估算杂散电容为3pF,通过计算得到外接电容30pF。但如果实际杂散电容高于预期,这一计算结果就会偏离真实需求。

什么时候杂散电容会超过3pF?

杂散电容超过3pF是非常常见的情况,例如:

MCU引脚电容较大,理想中是2pF,但是实际项目中可能会达到4~7pF。

当晶振与MCU之间距离较远时,走线长度带来的分布电容会迅速增加。每增加1cm走线,就可能增加0.2~1pF的额外电容。

在多层PCB中,如果晶振信号线紧贴地平面或电源层,还会形成类似平板电容的结构,这种耦合效应在四层及以上板子中尤为明显。

较大的焊盘设计或不合理的外接电容布局,也会进一步放大寄生效应。

……

杂散电容的影响

杂散电容对不同类型的晶振影响不同。对于无源晶振,它会改变等效负载电容,从而影响振荡频率、起振条件及稳定性;当负载电容偏大时,可能导致频率偏移甚至起振困难。

对于有源晶振,杂散电容不会直接影响输出频率,但可能通过影响走线、负载及电源环境,导致信号质量下降、抖动增加、边沿变差等。寄生参数与外部干扰的叠加,会进一步降低系统稳定性,表现为抖动增大和温度漂移特性变差。

凯擎小妹建议

在PCB设计阶段,通过合理布局可以有效控制杂散电容,例如:

将晶振尽量靠近MCU;

避免长走线或不必要的绕行;

尽量减少过孔数量;

在可靠性允许范围内缩小焊盘尺寸;

提供连续参考地,同时避免过强耦合;

远离DC-DC、高频时钟等干扰源等……

在实际项目中,杂散电容很少被直接测量。通常先基于经验值进行估算,并通过公式计算外接电容的初始值,随后结合实测频率和起振情况进行验证,最终通过微调电容值达到目标状态。

假设:谐振器CL为18pF,初始选用27pF电容,但测试发现频率偏低。结合现象判断杂散电容偏大,约为5pF,然后将电容调整为22pF后恢复正常工作。

KOAN晶振

若您需要针对具体应用的晶振选型建议和技术支持,欢迎随时联系我们,KOAN将为您提供专业、贴心的解决方案。我们提供无源晶振和有源晶振,覆盖多种规格尺寸,现货充足,以满足客户需求。我们的产品质量和技术处于行业领先水平。公司致力于精细化质量管理,以满足客户对高端产品的需求。

联系我们

销售:010-62101903

邮箱:sales@koan-xtal.com