发布时间:2025-12-26

发布时间:2025-12-26  阅读次数:664次

阅读次数:664次

在电子系统设计中,直观的想法往往是“需要多少频率,就选相应频率的晶振”。但在通信设备、处理器和高速数字系统中,我们更常见的方案却是:先选用一颗稳定的低频晶振,再通过倍频或PLL生成所需的高速时钟。这种设计并非多此一举,而是由晶振的物理特性和系统级稳定性共同决定的。

晶振的物理特性

石英晶体振荡器依赖石英的机械谐振特性工作。晶振频率越高,晶片就需要加工得越薄,对工艺精度、封装和环境的要求也随之提高。这不仅增加了制造难度,还会带来一致性下降、老化加快和稳定性变差等问题。

在工程实践中,几十MHz以内的晶振技术最成熟,频率稳定度高、相位噪声低、对电源和PCB布局也相对不敏感。而直接使用高频晶振,往往更容易受到电源噪声、负载变化和布线寄生参数的影响,反而不利于系统整体稳定。

倍频与锁相环的作用

为了在保证稳定度的前提下获得更高频率,现代高速系统几乎都依赖锁相环PLL进行频率合成。PLL以低频晶振作为参考源,通过闭环控制,使内部振荡器输出与参考频率保持固定倍数关系。一旦PLL锁定,高频时钟的长期频率准确度直接继承自参考晶振,而不取决于内部振荡器本身的绝对稳定性。

倍频系统中的晶振选择

从系统角度看,晶振并不是一个孤立的频率器件,而是整个时钟体系的基础。在倍频和频率合成应用中,更合理的思路是围绕系统瓶颈分层选择方案:

- 大多数应用优先选用低相位噪声晶振;

- 当温度变化或长期稳定性成为关键因素时,再在此基础上采用温补晶振TCXO。

- 低相位噪声晶振 -

参考源中的相位噪声和抖动,往往会随着倍频被一同放大。因此,在以低频晶振作为PLL参考源的系统中,优先选择低相位噪声、适合频率合成应用的晶振尤为关键。

KOAN有多款低噪声特性晶振可供选择:

- CMOS输出,LVDS输出,HCSL输出等。

- 温补晶振 -

在工业控制、户外通信或对长期频率一致性要求较高的应用中,温度变化往往成为主要挑战。普通晶振的频率会随温度漂移,当这种漂移影响系统性能时,就需要进一步提升参考源的温度稳定性。

温补晶振TCXO通过对晶体温度特性的补偿,使频率在较宽温度范围内保持更高一致性,从而提升整个倍频与频率合成系统在复杂环境下的可靠性。

KOAN晶振有各尺寸的温补晶振可供选择:

- 贴片1612,2016,2520,3225, 5032,7050;

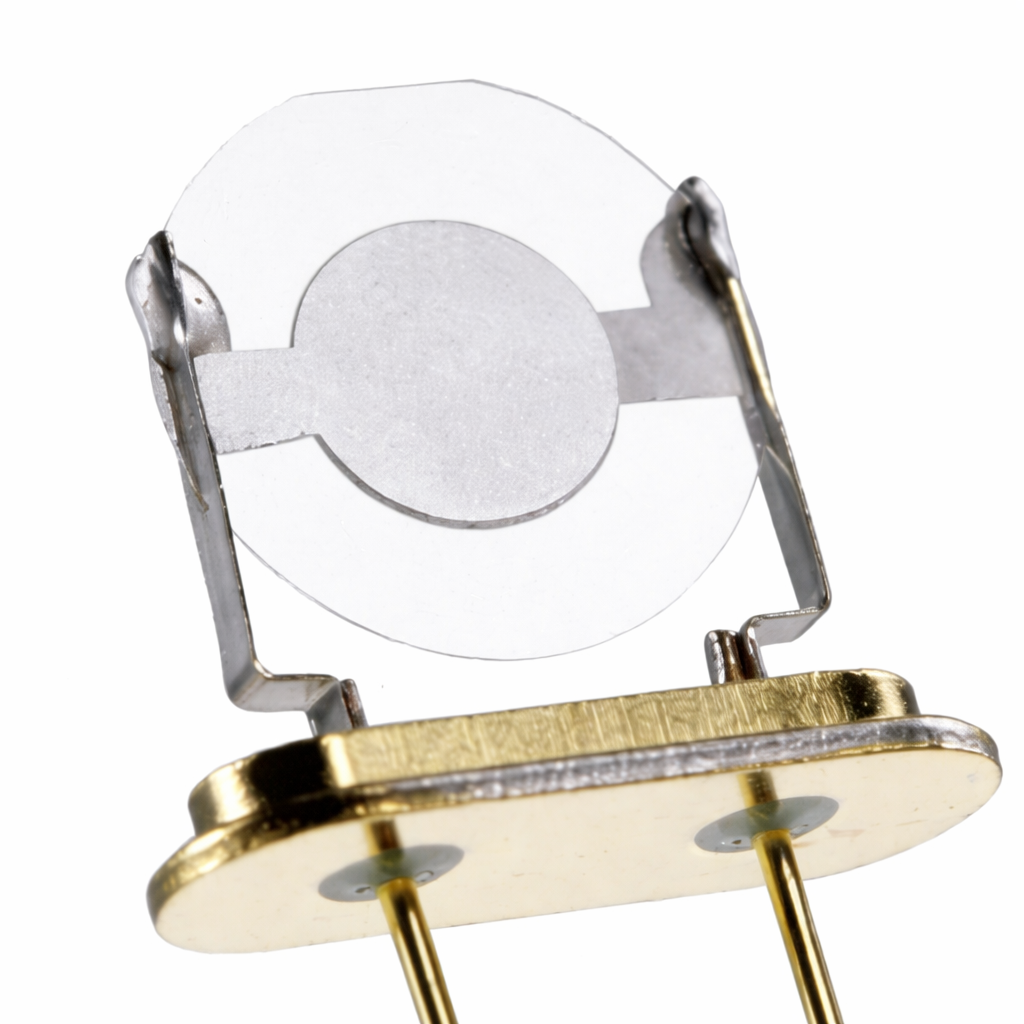

- 直插DIP14;

- CMOS输出,LVDS输出,True Sine输出,Clipped Sine输出等。

为了让设计与选型用户在选型时更高效,凯擎小妹在KOAN晶振官网的参数选择页面完善常用频率下拉列表,可快速选择,提高选型效率。如果您的设计需要列表之外的频率,也可以直接输入。

若您需要针对具体应用的晶振选型建议和技术支持,欢迎随时联系我们,KOAN将为您提供专业、贴心的解决方案。我们提供无源晶振和有源晶振,覆盖多种规格尺寸,现货充足,以满足客户需求。我们的产品质量和技术处于行业领先水平。公司致力于精细化质量管理,以满足客户对高端产品的需求。